The Korean Institute of Semiconductor Engineers believes the semiconductor industry could reach 0.2-nanometer-class chips by around 2040, ushering in what researchers call the “angstrom era.” The prediction appears in the group’s Semiconductor Technology Roadmap 2026, which outlines how chip scaling may continue over the next 15 years, even as traditional methods approach physical limits.

To put this into perspective, today’s most advanced commercial processes sit around 2nm, recently demonstrated by Samsung using its Gate-All-Around (GAA) transistor design. Moving to 0.2nm would represent a tenfold leap in node naming, though not a literal shrink of physical transistor size.

The Key Idea: Stacking, Not Shrinking

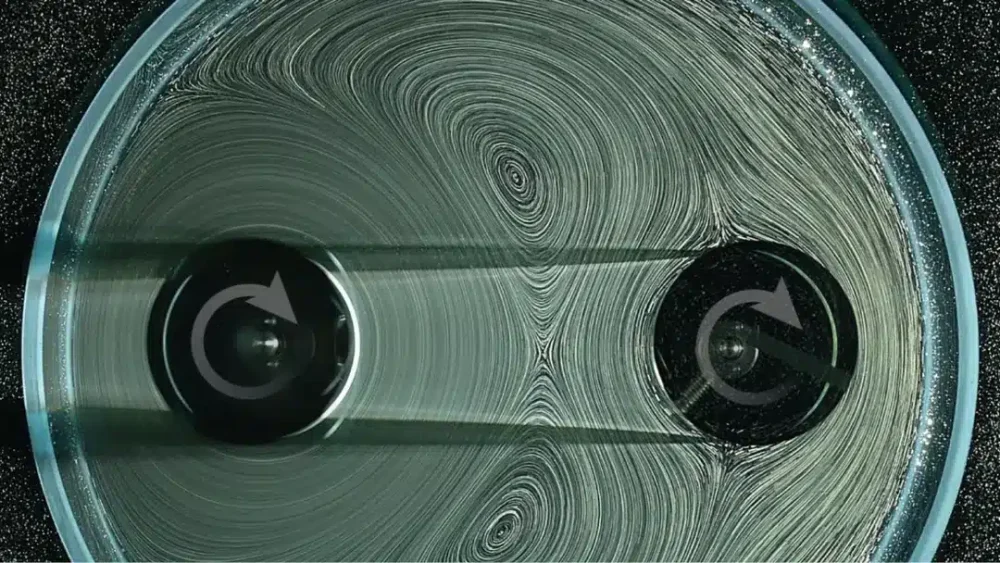

Instead of squeezing transistors closer together on a flat surface, future chips are expected to rely on monolithic 3D integration. This approach builds multiple layers of transistors on top of each other, dramatically increasing density without relying solely on smaller features.

A critical enabler of this shift is CFET (Complementary Field-Effect Transistor) technology, which vertically stacks n-type and p-type transistors. CFETs could overcome leakage and control problems that plague ultra-small transistors, making further scaling possible when conventional designs fail.

Progress Is Real, But Challenges Are Massive

Samsung has already moved beyond FinFETs with GAA at 2nm and is reportedly working on 1nm-class research, targeting mass production late this decade. Memory technologies are also expected to scale aggressively, with forecasts suggesting:

- DRAM shrinking from ~11nm to ~6nm

- High-Bandwidth Memory (HBM) growing from 12 layers to as many as 30 layers

- NAND flash scaling from hundreds to potentially 2,000 layers

AI processors are projected to leap from today’s tens of TOPS (trillion operations per second) to hundreds or even thousands of TOPS, driven by specialized architectures rather than raw transistor density alone.

Physics Is The Real Enemy

At these dimensions, engineers face problems that can’t be solved by better lithography alone. Silicon atoms are roughly 0.2nm in size, meaning a “1nm-class” transistor spans only a handful of atoms. This introduces severe issues such as quantum tunneling, electrical noise, heat density, and unreliable insulation.

As a result, future chips will likely combine:

- New transistor structures (GAA, CFET, vertical devices)

- Advanced materials beyond pure silicon

- Extreme ultraviolet (EUV) and high-NA EUV lithography

- Advanced packaging and chiplet designs, rather than single massive dies

Node Names No Longer Mean What They Used To

The institute also acknowledges a growing industry reality: node labels like 2nm or 1nm are no longer literal measurements. Instead, they represent improvements in performance, power efficiency, and density, not the physical length of a transistor.

This is why companies like TSMC, Samsung, and Intel can all claim similar “nodes” while using very different technologies under the hood.

The Takeaway

Reaching 0.2nm-class technology by 2040 is not science fiction, but it won’t come from simple shrinking. Progress will depend on 3D transistor stacking, new materials, and architectural innovation, not just smaller geometries. The angstrom era may arrive, but it will look very different from the Moore’s Law playbook that built the modern computing world.