At IEDM 2024, Intel Foundry’s Technology Research team demonstrated industry-first advancements in transistor and packaging technologies that help meet future demands for AI.

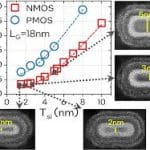

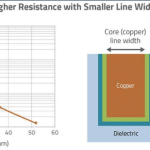

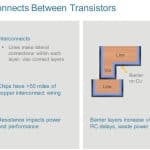

At the IEEE International Electron Devices Meeting (IEDM) 2024, Intel Foundry unveiled breakthroughs to help drive the semiconductor industry forward into the next decade. Intel Foundry showcased new material advancements that help improve interconnections within a chip, resulting in up to 25% capacitance using subtractive ruthenium. Intel Foundry was also the first to report a 100x throughput improvement using a heterogeneous integration solution for advanced packaging to enable ultra-fast chip-to-chip assembly. To further drive gate-all-around (GAA) scaling, Intel Foundry demonstrated work with silicon RibbonFET CMOS and gate oxide module for scaled 2D FETs for improved device performance.

“Intel Foundry continues to help define and shape the roadmap for the semiconductor industry. Our latest breakthroughs underscore the company’s commitment to delivering cutting-edge technology developed in the U.S., positioning us well to help balance the global supply chain and restore domestic manufacturing and technology leadership with the support of the U.S. CHIPS Act.”